Hi,

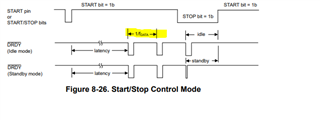

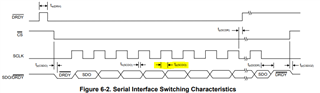

In start/stop control mode, is there a formula to calculate the time between ~DRDY going low (indicating data ready) to the shift register being filled with the next bin of samples? If not, can you please tell me how I can roughly estimate the time between these two events?

Thank you,

Alex