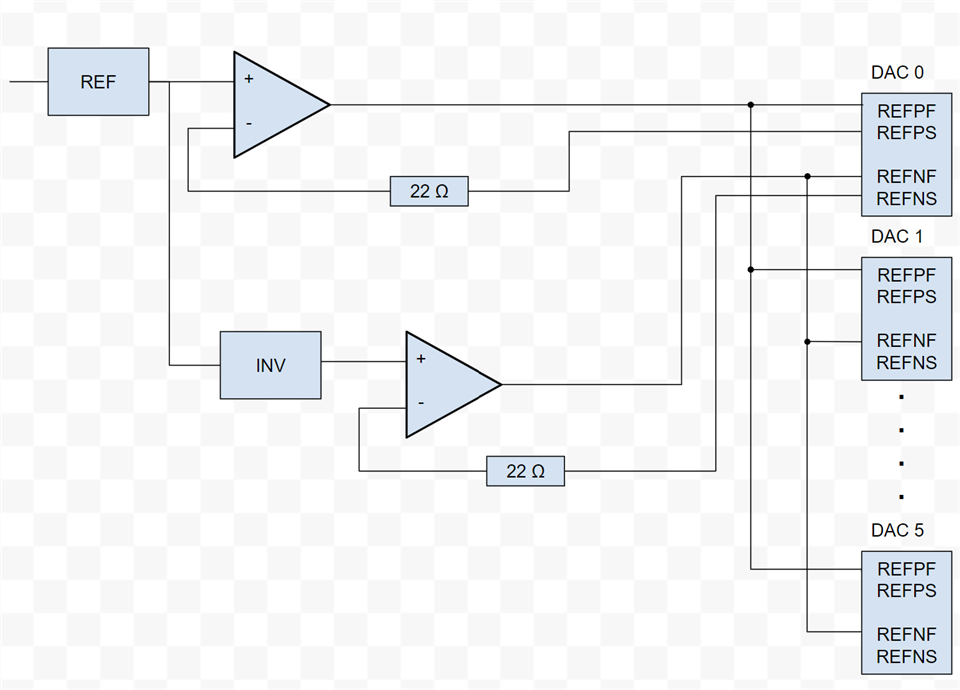

We currently have a PCB with once reference supplying 6 DAC11001A devices on a board. We only have one sense connection circuit for all 6 of these DACs (there was not room for multiples of these circuits). We are finding that the DACs without the sense connection are performing in a nonlinear fashion that is outside the datasheets specs. This is our setup:

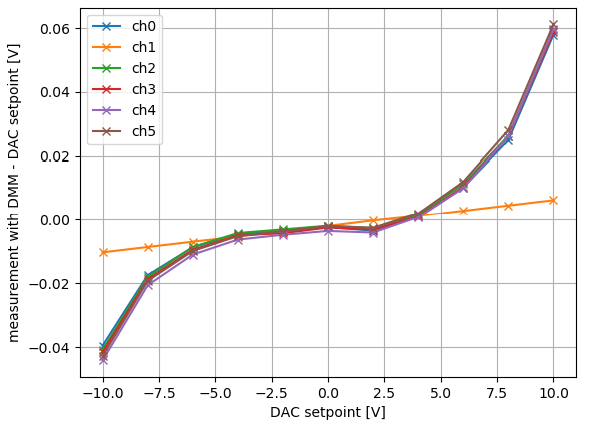

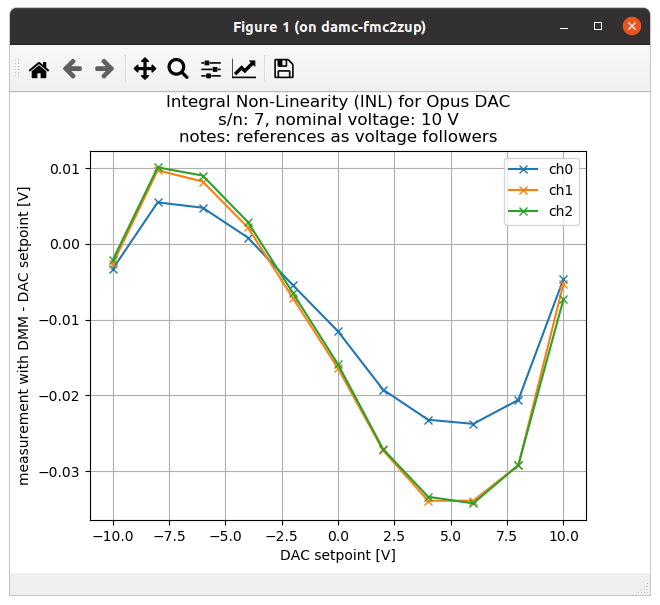

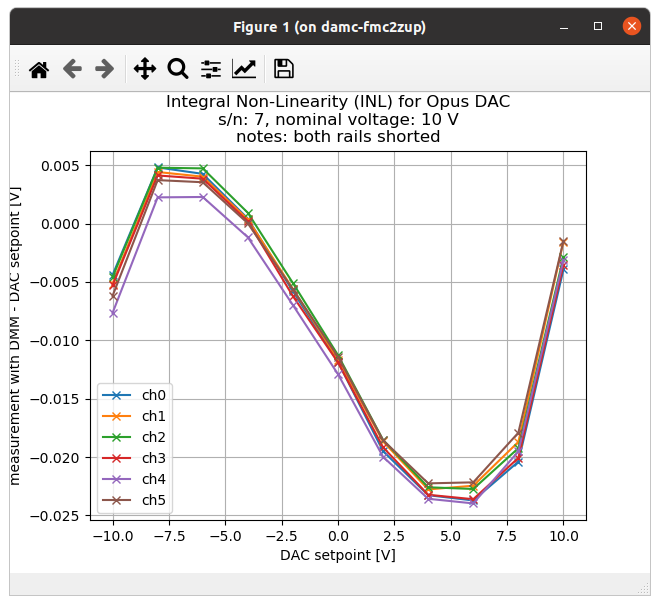

DAC0 is furthest away from the reference in the layout and is connected to the sense circuitry. We have experimented and found that if we connect the sense line to any other DAC, that DAC becomes the more linearly behaving one and the rest are nonlinear (see image below with test data). Is there a way that we can configure this to be more linear on all DACs without respinning the board? Thanks in advance!