Other Parts Discussed in Thread: ADS1148

I'm working on an application where I need to have the sample rate be a multiple of the input frequency.

I saw the data sheet indicates the sync signal is different than a traditional trigger/convert start input, but I only needed a max sample rate of about 4100Hz so I figured I could use the global-chop mode and the sync pin to act more like a trigger input since global-chop waits to send the DRDY signal until the filters have flushed and the data is correct.

I calculated this method should allow about 5k sample rate as follows:

fMOD = 4.096MHZ

tMOD = 0.24415 usec

tGC_DLY = 2 tMOD

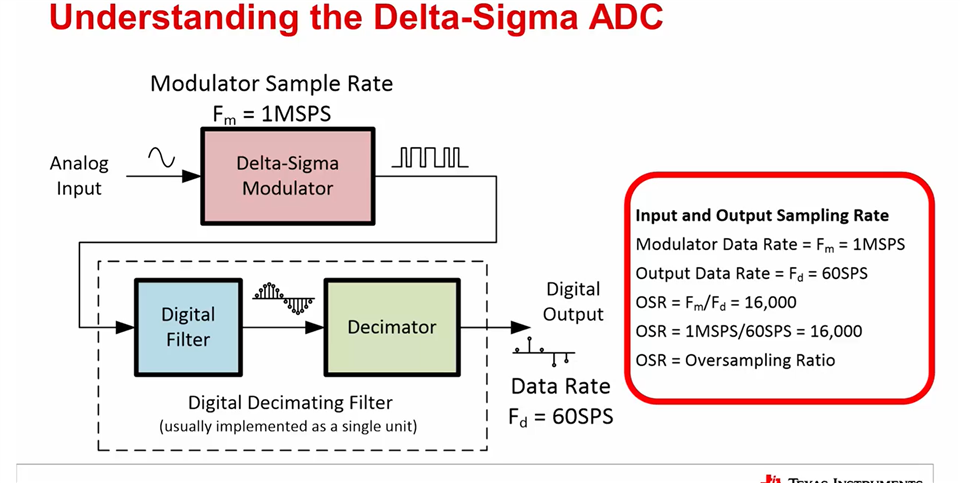

OSR = 128

tGC_FIRST_CONVERSION = tGC_DLY + 3 × OSR x tMOD + tGC_DLY + 3 × OSR x tMOD + 44 x tMOD

= 2(tGC_DLY + 3 × OSR x tMOD) + 44 x tMOD

= 4 x tMOD + 768 x tMOD + 44 x tMOD

= 816 x tMOD

= 199.2 usec or 5020Hz

However, the MCU is taking too long to read the data and I'm seeing an effective sample rate of about 4000Hz. It may be an issue with FW, but I wanted to clarify what happens when the data is not yet read and the sync pin is toggled. Can a currently started read transaction be completed, or is FIFO cleared which corrupts the results?

So far I've avoided trying to use continuous-conversion mode with the sync pin due to the need to read and discard data while the filter is settling, but it should theoretically be faster. Is there any way to get the first "settled" sample without burdening the MCU with extra SPI transactions?

Is there any other method I'm missing that would allow a variable sampling rate on this chip?

Also - we selected this part due to price point & need the PGA and 8 inputs, but we really don't need a full 24-bit resolution. Are there other parts for a similar price that meet the application needs better?

Thanks!