Other Parts Discussed in Thread: ADS124S08,

Hi team,

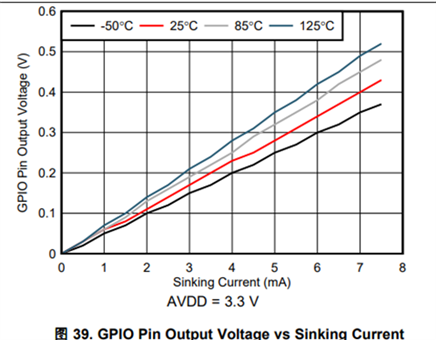

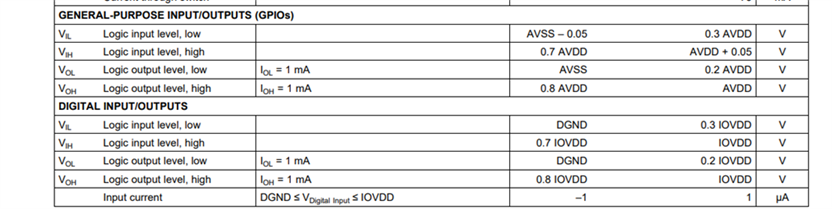

We use ADS114S08 and ADS124S08 to drive MOS, in the datasheet write" Vol MAX arrived at 0.2*AVDD, when IOL = 1mA". But now our MOS Gate leakage current only have 10uA, Vth= 0.3~ 0.7V, we want to know what the maximum VoL at this time is. We must require MOS is turn off when GPIO is Low level. Please help to check whether it is feasible.

I'm looking forward to your reply soon!

Best regards, Hao

EC, FAE