Hello.

I want to receive the output of ADS8681 in 1 MHz cycles

I am inquiring about the SPI configuration for the maximum output of ADS8681(1 MHz).

In the datasheet, maximum SPI clock is 66.67MHz(about 15ns).

Using the maximum clock, It takes 480ns(15ns * 32) to receive 32-bit output in single SDO. And maximum conversion time is 665 ns.

Even if some additional delay is not considered, (480 + 665)ns exceeds 1000ns(1Mhz).

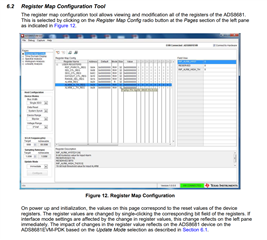

But, in the figure 12 of ADS8681EVM-PDK user manual, it is explained that maximum sampling rate is possible in condition of single SDO and 66MHz SPI clock.

Please check if I'm mistaken.

Also, I would appreciate it if you could tell me how to configure SPI to achieve maximum sampling rate(1 MHz).

Thanks.