Other Parts Discussed in Thread: ADS1278, , ADS1178

Hello,

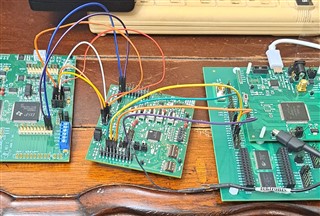

I interfaced to ADS1278 EVM from a Cortex-M4 processor via SPI. I am using the MMB0 to provide power, CLK, and reference voltages to ADS1278EVM. Before I apply power to the MMB0 EVM, I would like to confirm this approach please.

Text highlighted is either a question or I am looking for concurrence. Both are located either in far-right column of a table or located within text indicated with a “•”

ADS1278EVM is physically removed from the ADS1278EVM-PDK

- MMB0 is used as a power source to power the ADS1278EVM

- Used S2 switch to set MODE, FORMAT, and CLKDIV lines, used S1 switch to power all 8 ADC channels, used default S3 switch setting for 27MHz to clock ADS1278

Below is a visual of what I described above. Tables follow with detail of connections.

|

S1 |

All ON (UP) |

Power all 8 ADC channels |

|

|

S2 |

(SPI, TDM, Dynamic) F0, F1, F2 ALL “OFF” (MODE [10]) M0 “OFF” M1 “ON” CLKDIV [0] “OFF” |

MODE, FORMAT, and CLKDIV lines |

|

|

S3 |

INT (Right) |

Using Onboard Oscillator to clock ADS1278EVM |

Using buffered on-board |

|

S6 |

Serial Interface format |

FS - Frame Sync format. [1-2], [4-5], [7-8], [10-11] SPI - SPI-compatible mode. [2-3], [5-6], [8-9], [11-12] |

I JUMPED for SPI-compatible mode so, |

|

JP1 |

Short |

FSX IS connected to SYNC/DRDY |

I SHORTED this? |

|

JP2 |

Open |

FSR NOT connected to SYNC/DRDY |

I OPENED this? UG states only one can be selected |

Critical Standalone Connections:

|

Function |

EVM Header/Pin |

MMB0 Header/Pin |

Cortex-M4 Header/Pin |

Pin Name |

Description |

|

|

|

SCLK |

J4.3 |

|

SPI2_SCK |

CLKX |

SCLK |

|

Interface |

DIN |

J4.11 |

|

SPI2_MOSI |

DX |

Data In |

|

|

DOUT |

J4.13 |

|

SPI2_MISO |

DR |

Data Out |

|

|

DRDY (SPI) |

J4.15 |

|

PORTF [10] |

INT |

DRDY/FSYNC |

|

|

1.8V |

J5.7 |

J5.7 |

|

+1.8VD |

Digital supply |

|

Power |

3.3V |

J5.9 |

J5.9 |

|

+3.3VD |

Digital supply |

|

|

5.0V |

J5.3 |

J5.3 |

|

+5VA |

Analog supply |

|

Analog Inputs |

Channels 1-4 |

J3.1-8 |

|

|

|

Analog Inputs |

|

|

Channels 5-8 |

J1.3-10 |

|

|

|

Analog Inputs (ADS1178 and ADS1278 only) |

|

Ground Connections |

||||||

|

|

DGND |

J5.5 |

J5.5 |

|

DGND |

Digital ground |

|

Ground |

AGND |

J5.6 |

J5.6 |

|

AGND |

Analog ground input |

|

|

DGND |

J4.4 |

|

TP2 GND |

|

Is this the correct BOARD/PIN to hook the Cortex-M4 TP2 GND to? |

|

Voltage Reference |

||||||

|

Reference Voltage |

REFN |

J3.18 |

J7.18 |

|

|

Analog Inputs |

|

Reference Voltage |

REFP |

J3-20 |

J7.20 |

|

|

Analog Inputs |

Analog Inputs

The analog inputs for the ADS1278EVM are connected to J1 and J3. Will connect four devises to Channels J3 1-4 according to sensor datasheet. S4, S5, S7, and S8 default to unbuffered signal.

Voltage Reference

Switch S3 selects the reference voltage from the buffered REF5025 and is connected to reference pins:

J3.18 = REFN and J3.20 = REFP - supplied by MMB0 motherboard

|

Mode [1:0] |

Mode Selection |

CLKDIV |

Max fCLK |

fMOD |

Max fMOD |

OSR |

fCLK/fDATA |

Max fDATA |

|

10 |

Low-Power |

0 |

13.5MHz |

fCLK/1 |

13.5MHz |

64 |

256 |

52.734kSPS |

Will this work?

Is it safe?

What have I not thought of?

Thanks,

William