Other Parts Discussed in Thread: LMK04828

Hi there,

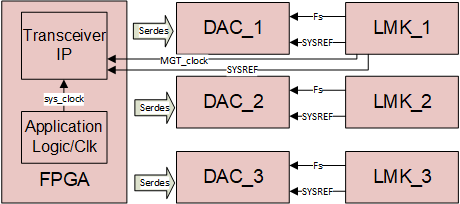

I have multiple DAC39J84 ICs to be synchronized. Each DAC39J84 is clocked by an LMK04828.

In a related thread, ±1 VCO cycle error for LMKs' output device clock aligning was found when performing multiple-LMK synchronization.

Based on this, I found multiple DAC39J84 outputs were not synchronized at the same position after each power cycle, which means I didn't realize the deterministic latency. I am not sure if it is related to the previous LMK sync issue.

The DAC39J84 runs at 1GHz. The JESD204B (subclass 1) parameters are as follows:

L = 8 // Number of lanes M = 4 // Number of converters per link F = 1 // Number of octets per frame per lane S = 1 // Number of converter samples per frame K = 32 // Number of frames per multiframe HD = 1 // High Density N = 16 // Number of bits per sample N_prime = 16 // Number of adjusted bits per sample

My DAC39J84 register settings are:

(0x00,0x0018) (0x4a,0xff1e) (0x01,0x00a0) (0x02,0x2082) (0x1a,0x0020) (0x24,0x0020) (0x25,0x2000) (0x3b,0x0800) (0x3c,0x0228) (0x3d,0x0088) (0x3e,0x0108) (0x3f,0x005a) (0x4b,0x0700) (0x4c,0x1f07) (0x4d,0x0300) (0x4e,0x0f4f) (0x51,0x00df) (0x5c,0x1122) (0x5f,0x7654) (0x60,0x3210) (0x61,0x0001) (0x4a,0xff1f) (0x4a,0xff01)

My question is: can we realize the deterministic latency and synchronize multiple DAC39J84 ICs after each power cycle, with the presence of ±1 VCO cycle error for LMK device clock?

I was thinking that the ±1 cycle device clock error was not dominating in the JESD204B protocol, if we can ensure the SYSREF to align LMFCs.

Can you help check if anything is missing in the DAC39J84 register setting?

Thanks and best,

Yilun