Hi Team,

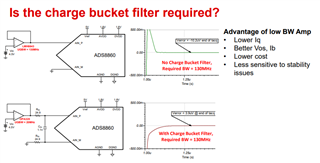

I would like to ask for clarification for this video slide-7, how is it estimated that 130MHz BW is required for op-amp if no charge bucket filter is used?

Here is the video link: training.ti.com/ti-precision-labs-adcs-introduction-sar-adc-front-end-component-selection

I hope you can help.

Regards,

Marvin