Hello,

My application requires the capture of samples from four ADC3444s by an FPGA. I have some concerns regarding the synchronicity of the ADCs and whether it will be possible to time correlate the samples.

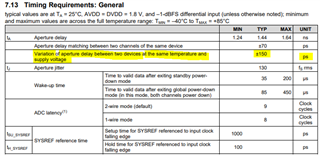

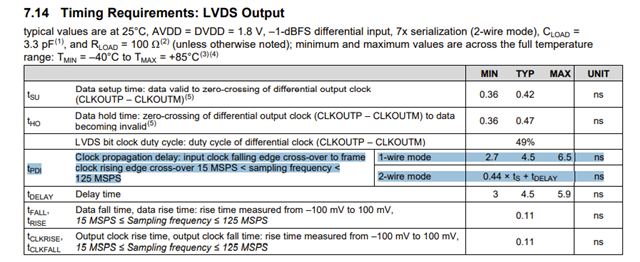

Each of the four ADCs receive the same 125 MHz sampling clock and will run in 2-wire mode. How can I ensure that the conversions of each ADC are synchronized ? Similarly, what's the worst case phase difference among each ADCs DCLKs and FCLKs, and could this make the temporal correlation of samples from each ADC within the FPGA problematic ? Can the SYSREF pin be leveraged in order to ensure synchronicity of the data ?

Thank you.