Dear, support Team.

We are having trouble writing SCLK to the ADS1256.

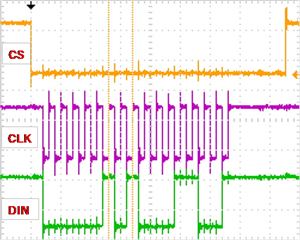

Our SCLK starts HI, not LO.

This is controlled by an LSI separate from the SPI interface.

For example, can reset timing using SCLK be reset without the rising edge of SCLK?

Best Regards,

Hiroaki Yuyama

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.