Hi,

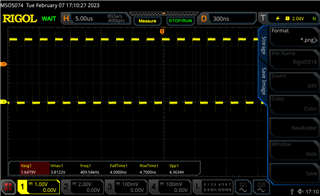

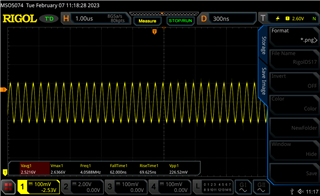

I built a EKG device with the ADS1293 and I have trouble to get correct readings. I can correctly write and read back registers over SPI, so this should not be the issue. I set up the Testing modes for the ADC, but I get only garbage values out of it (random). So I measured all the signals and so far everything looks good (CVREF is perfectly 2.4V), except I'm unsure about the oscillator. The signal seems to have an offset of around 3V and only swings with an amplitude of around 100mV. I tried different load caps but could not really change the behaviour at all, so I think that might be an issue. When I deactivate the external crystal over SPI, I do not get readings at all.

What amplitude should the XTAL CLK show when running correctly? Might the layout be an issue here (I gave 20mil clearance for the XTAL nets and so far I never had any issues with crystals in microcontroller applications, but I might have removed the GND plane underneath it?

So, is the CLK signal incorrect here (Measured with a x10 Probe):

Edit:

Problem solved, there was a wrong connection from the supply.