Hello,

I am relatively new to setting up and debugging SPI communication, so I appreciate your patience in advance.

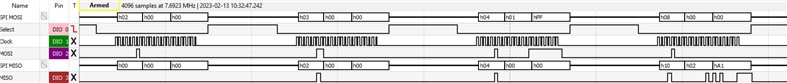

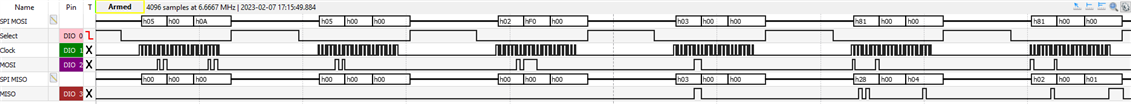

I've reflowed the DAC60508 to my board and tried to read the DEVICE ID unsuccessfully. I've verified the SPI mode to be correct, in mode 1, verified below. I checked the forums here and saw other comments recommending writing to the TRIGGER register to perform a soft reset, clearing the LDAC, writing to the SYNC register to clear BRDCAST enables, and clearing the CONFIG register to make sure FSDO is 0, despite that being the default value.

Subsequent SPI access cycles with the same MOSI bytes as above will return semi-stable but nonsensical values from the DAC, none of which are the DEVICE ID or even an echo of the first byte from the previous access cycle.

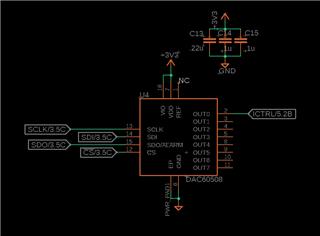

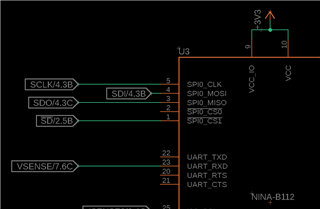

Here's the DAC schematic for my board:

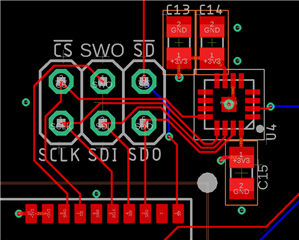

I am currently debugging with a nRF52840, no lines are pulled up on the SPI, but the DAC is the only interfaced SPI device. I don't believe this would be the issue, but again I'm a bit new to this so it could be!

Any help would be greatly appreciated!