Other Parts Discussed in Thread: DAC37J82EVM, DAC37J82,

Hi TI team,

I got two EVMs on the hand TSW14J56+DAC37J82. According to the DAC37J82EVM user guide, I can make the quick-start prodedure succesfully.

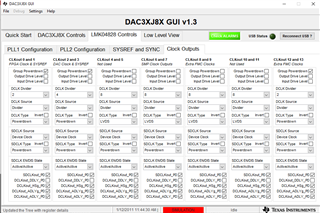

We use LMF=222 configuration for the DAC37J82.

In the next step, we want to make a copy of this JESD204B project in our own prototype. We are using ZYNC7000 FPGA now.

Could you please let me know your JESD204B configurations based on this quick-start prodedure? Both on FPGA and DAC side are appreciate.

And we still need TI JESD204B IP in our design.

Best Regards,

Brooke