Other Parts Discussed in Thread: ADC12QJ800

Hi Team,

I'm using the ADC12QJ800 chip's JMODE0 mode to collect data. Could you tell me how to splice the data received by the FPGA receiving end to obtain the sampling data?

Kind regards,

Katherine

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Team,

I'm using the ADC12QJ800 chip's JMODE0 mode to collect data. Could you tell me how to splice the data received by the FPGA receiving end to obtain the sampling data?

Kind regards,

Katherine

Could you tell me how to splice the data received by the FPGA receiving end to obtain the sampling data?

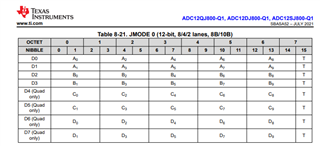

According to the JMODE0 mode, I'll use the corresponding relation between the data received by the ADC FPGA receiver JESD IP and the 12bit data sent by the ADC.

Hi Katherine,

Here is the tranport layer table from the datasheet which can be used to see how data to the FPGA in JMODE0.

Regards,

Neeraj