Hi,

Good Day.

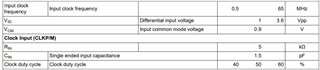

We need to know the Differential Signal Level for CLKP and CLKM.

Datasheet doesn't mention what is common mode required on the differential clock input.

We need to know the levels of all the differential signals' input and output.

Please advise. Thank you very much.

Best Regards,

Ray Vincent