We are trying to establish a connection between Polarfire FPGA XCVR RX and ADC12DJ3200EVM.

DUT(FPGA) configurations: FPGA XCVR is configured to 5000Mbps, expecting CDR ref clock as 125MHz and JESD RX soft IP is configured based on the JMODE settings mentioned in the UG of ADC12DJxx00.

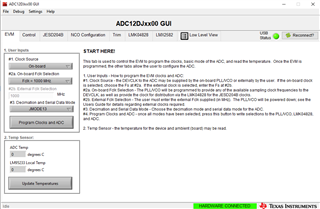

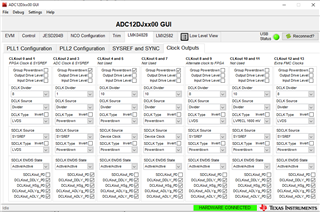

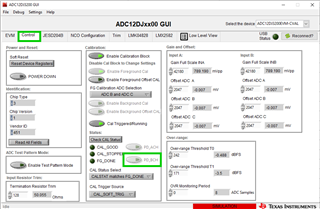

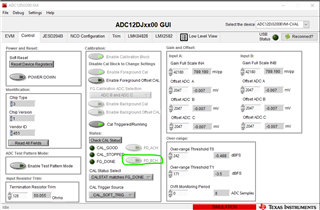

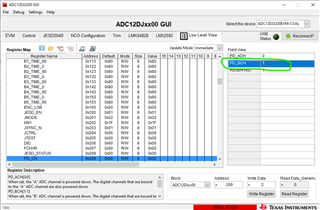

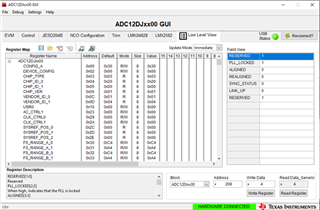

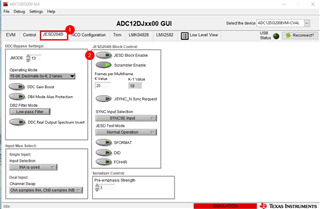

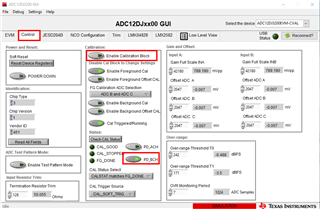

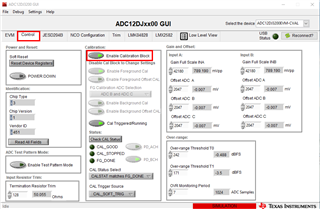

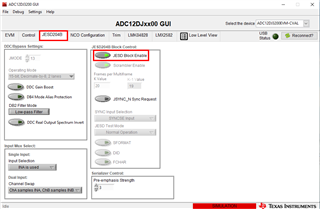

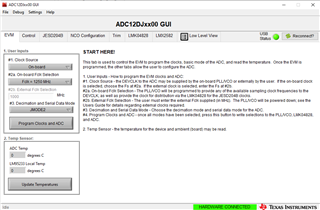

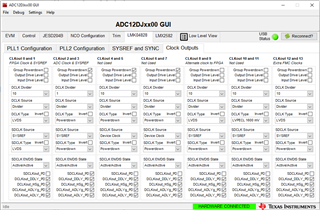

ADC configurations:

JMODE2: Providing the configurations used for JMODE2 (Remaining tabs are left as it was to provide default configurations)

-

-

- Onboard Fclk selection (Fclk) = 1250MHz, DCLK divider = 10 --> Output clock from ADC = 125MHz

- For JMODE2 we are observing expected behavior (For LMFS = 4485).

- Note: Also instead of L = 4, when we configure L = 1 we are not seeing the expected behavior. Is there a way we can use the ADC in single lane mode in JMODE2(For LMFS = 1485)?

JMODE13:

- For JMODE13, we are unable to make the link work.

Please let us know if we are missing anything here.

Thanks.