Other Parts Discussed in Thread: AMC7834

Hi expert,

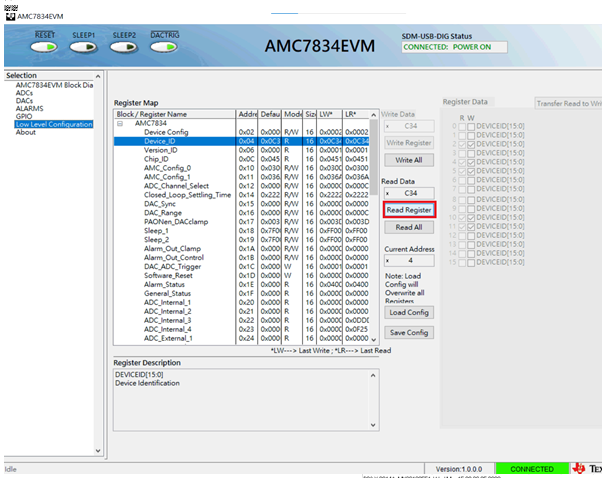

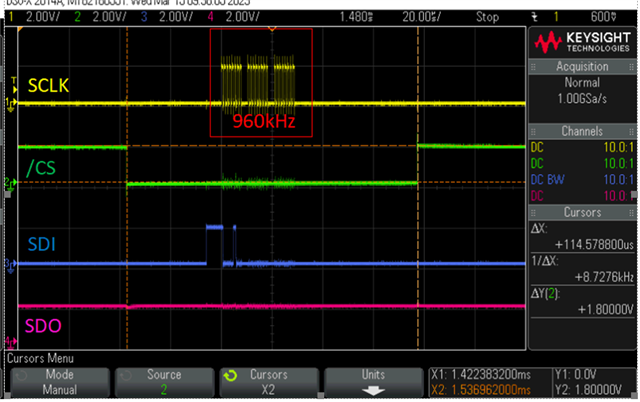

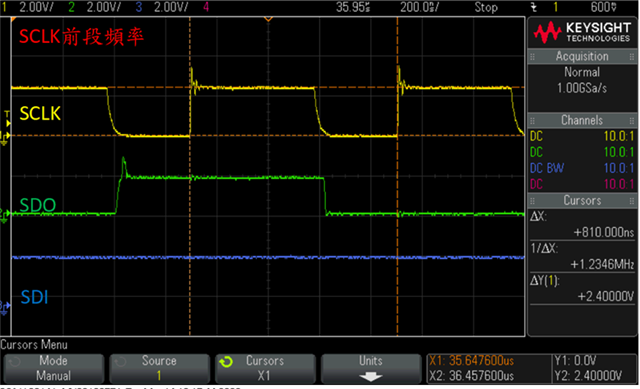

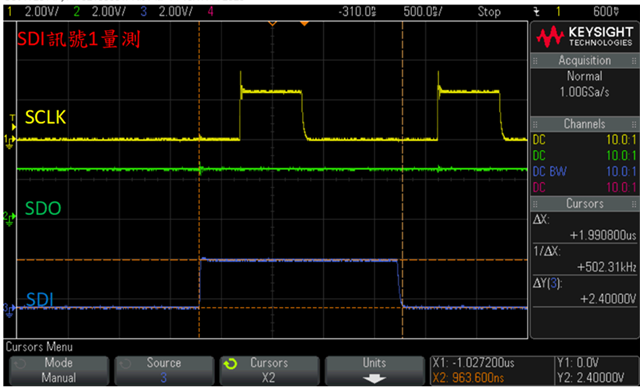

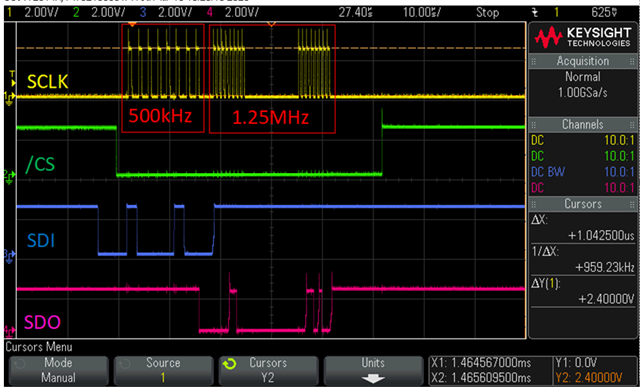

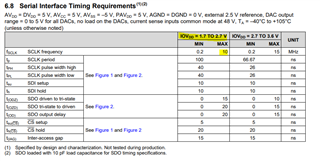

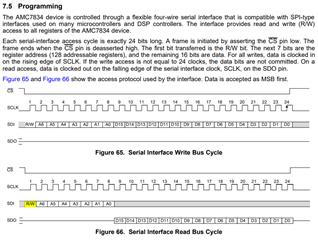

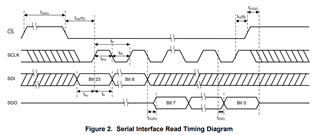

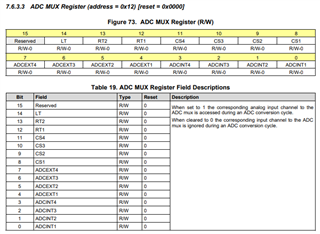

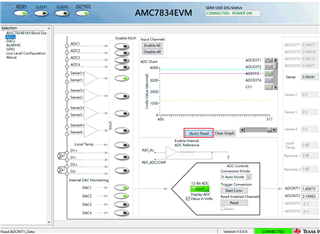

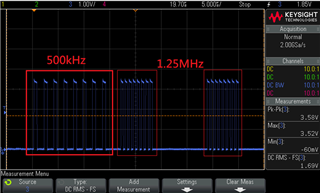

Customer measure SPI CLK on the EVM, it shows two different clock rates, 500Khz and 1.25Mhz as (Auto) Read is marked. Could you please explain why?

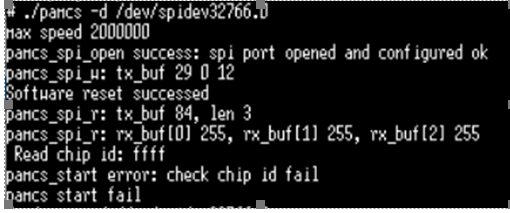

The reason why I am asking is because customer now can't read registers with their driver. So wondering what might goes wrong.

Regards,

Allan