Hi Team,

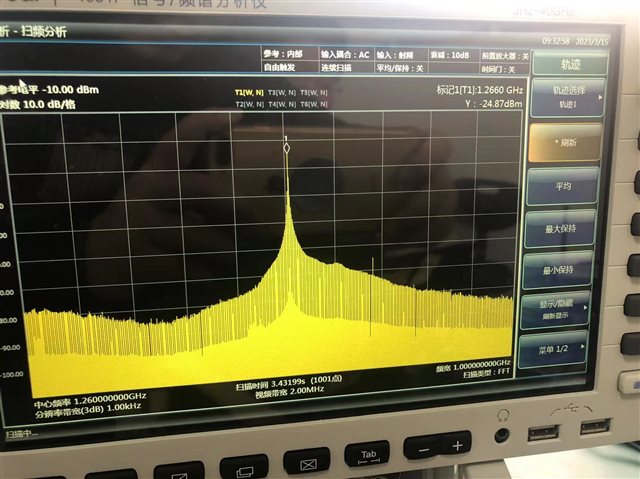

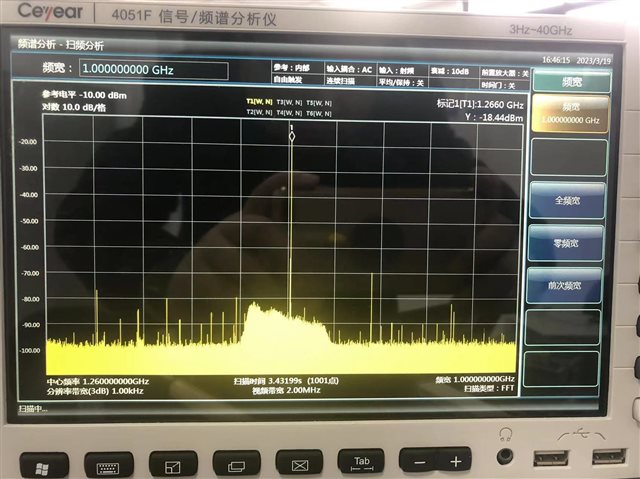

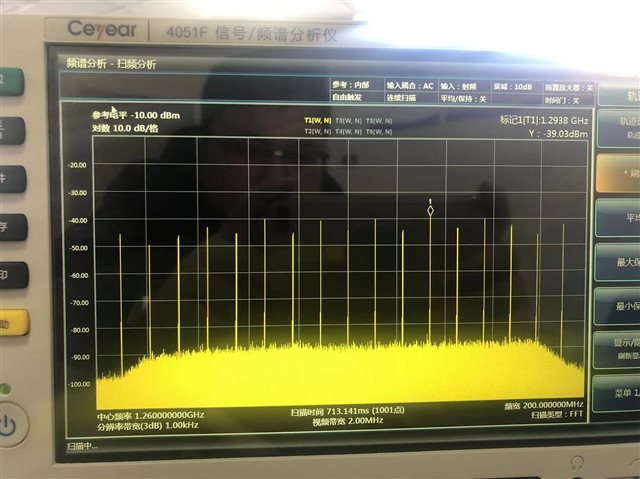

I don't have an EVM board, and I am using a self-made board to debug the DAC38RF84, and now I have a strange problem. I use FPGA to generate a 64-point sine signal (I channel) and cosine (Q channel). Each sampling point is 16 bits, and I send it to DAC at the rate of 360M MPS for I and Q respectively. But the output of the DAC is a multi-frequency spectrum, not a single-frequency spectrum. The frequency spectrum appears periodically at the frequency of sine (5.625MHZ) as shown in the picture below. I am confused why there are so many frequencies?

I used CLK_P/N as the clock input with a frequency of 180MHz. LMFSHD = 82121, 16x Interpolation.K=32. SYSREF is set to 2.8125MHz, LANE RATE =1800MHZ, sampling frequency is 5760MHz, only NCO1 is used, the frequency of NCO1 is configured as 1.26GHZ, and 1 pair of IQ inputs. The PLL clock and SERPLL clock are also locked. The following is my register configuration table.

// Addr Value

{0x0000U, 0x7863U}, // 0 Reset

{0x0000U, 0x7860U}, // 1 Reset

{0x0001U, 0x3081U}, // 2 Config 4-wire mode

{0x0002U, 0x0000U}, // 3

{0x0003U, 0x0000U}, // 4

{0x0004U, 0x00FEU}, // 5

{0x0005U, 0x0000U}, // 6

{0x040AU, 0x7C03U}, // 7

{0x040BU, 0x0002U}, // 8

{0x040CU, 0xA002U}, // 9

{0x040DU, 0xF000U}, // 10

{0x041BU, 0x0100U}, // 11

{0x0423U, 0xFFFFU}, // 12

{0x0424U, 0x1001U}, // 13

{0x0431U, 0x0400U}, // 14

{0x0432U, 0x0708U}, // 15

{0x0433U, 0x333CU}, // 16

{0x0434U, 0x0000U}, // 17

{0x0435U, 0x0018U}, // 18

{0x043BU, 0x9802U}, // 19

{0x043CU, 0x8229U}, // 20

{0x043DU, 0x0088U}, // 21

{0x043EU, 0x0949U}, // 22

{0x043FU, 0x0000U}, // 23

{0x010AU, 0x4810U}, // 24

{0x010CU, 0x4620U}, // 25

{0x010DU, 0x1300U}, // 26

{0x010EU, 0x00FFU}, // 27

{0x010FU, 0xFFFFU}, // 28

{0x0110U, 0xFFFFU}, // 29

{0x0111U, 0xFFFFU}, // 30

{0x0117U, 0x0000U}, // 31

{0x0119U, 0x0001U}, // 32

{0x011CU, 0x0000U}, // 33

{0x011DU, 0x0000U}, // 34

{0x011EU, 0x0000U}, // 35

{0x011FU, 0x0000U}, // 36

{0x0120U, 0x3800U}, // 37

{0x0121U, 0x0000U}, // 38

{0x0122U, 0x0000U}, // 39

{0x0123U, 0x0000U}, // 40

{0x0124U, 0x0030U}, // 41

{0x0125U, 0xB700U}, // 42

{0x0127U, 0x2222U}, // 43

{0x0128U, 0x0330U}, // 44

{0x0129U, 0x0000U}, // 45

{0x012AU, 0x0000U}, // 46

{0x012BU, 0x0000U}, // 47

{0x012CU, 0x0000U}, // 48

{0x012DU, 0x1FFFU}, // 49

{0x012EU, 0x1FFFU}, // 50

{0x012FU, 0x0000U}, // 51

{0x0130U, 0x0200U}, // 52

{0x0132U, 0x0400U}, // 53

{0x0133U, 0x0400U}, // 54

{0x0146U, 0x0044U}, // 55

{0x0147U, 0x190AU}, // 56

{0x0148U, 0x31C3U}, // 57

{0x014AU, 0xFF03U}, // 58

{0x014BU, 0x1300U}, // 59

{0x014CU, 0x1F07U}, // 60

{0x014DU, 0x0101U}, // 61

{0x014EU, 0x0F4FU}, // 62

{0x014FU, 0x1C60U}, // 63

{0x0150U, 0x0000U}, // 64

{0x0151U, 0x00FFU}, // 65

{0x0152U, 0x00FFU}, // 66

{0x0153U, 0x0100U}, // 67

{0x0154U, 0x8E60U}, // 68

{0x015CU, 0x0002U}, // 69

{0x015EU, 0x0000U}, // 70

{0x015FU, 0x3210U}, // 71

{0x0160U, 0x7654U}, // 72

{0x0164U, 0x0000U}, // 73

{0x0165U, 0x0000U}, // 74

{0x0166U, 0x0000U}, // 75

{0x0167U, 0x0000U}, // 76

{0x0168U, 0x0000U}, // 77

{0x0169U, 0x0000U}, // 78

{0x016AU, 0x0000U}, // 79

{0x016BU, 0x0000U}, // 80

{0x016CU, 0x0000U}, // 81

{0x016DU, 0x0000U}, // 82

{0x016EU, 0x0000U}, // 83

{0x020AU, 0x8810U}, // 84

{0x020CU, 0x2402U}, // 85

{0x020DU, 0x0000U}, // 86

{0x020EU, 0x00FFU}, // 87

{0x020FU, 0xFFFFU}, // 88

{0x0210U, 0xFFFFU}, // 89

{0x0211U, 0xFFFFU}, // 90

{0x0217U, 0x0000U}, // 91

{0x0219U, 0x0001U}, // 92

{0x021CU, 0x0000U}, // 93

{0x021DU, 0x0000U}, // 94

{0x021EU, 0x0000U}, // 95

{0x021FU, 0x0000U}, // 96

{0x0220U, 0x0000U}, // 97

{0x0221U, 0x0000U}, // 98

{0x0222U, 0x0000U}, // 99

{0x0223U, 0x0000U}, // 100

{0x0224U, 0x0020U}, // 101

{0x0225U, 0xB700U}, // 102

{0x0227U, 0x8888U}, // 103

{0x0228U, 0x0330U}, // 104

{0x0229U, 0x0000U}, // 105

{0x022AU, 0x0000U}, // 106

{0x022BU, 0x0000U}, // 107

{0x022CU, 0x0000U}, // 108

{0x022DU, 0x1FFFU}, // 109

{0x022EU, 0x1FFFU}, // 110

{0x022FU, 0x0000U}, // 111

{0x0230U, 0x0000U}, // 112

{0x0232U, 0x0400U}, // 113

{0x0233U, 0x0400U}, // 114

{0x0246U, 0x0044U}, // 115

{0x0247U, 0x190AU}, // 116

{0x0248U, 0x31C3U}, // 117

{0x024AU, 0x0003U}, // 118

{0x024BU, 0x1300U}, // 119

{0x024CU, 0x1307U}, // 120

{0x024DU, 0x0101U}, // 121

{0x024EU, 0x0F4FU}, // 122

{0x024FU, 0x1C60U}, // 123

{0x0250U, 0x0000U}, // 124

{0x0251U, 0x001FU}, // 125

{0x0252U, 0x00FFU}, // 126

{0x0253U, 0x0100U}, // 127

{0x0254U, 0x8E60U}, // 128

{0x025CU, 0x0003U}, // 129

{0x025EU, 0x0000U}, // 130

{0x025FU, 0x3210U}, // 131

{0x0260U, 0x5764U}, // 132

{0x0264U, 0x0000U}, // 133

{0x0265U, 0x0000U}, // 134

{0x0266U, 0x0000U}, // 135

{0x0267U, 0x0000U}, // 136

{0x0268U, 0x0000U}, // 137

{0x0269U, 0x0000U}, // 138

{0x026AU, 0x0000U}, // 139

{0x026BU, 0x0000U}, // 140

{0x026CU, 0x0000U}, // 141

{0x026DU, 0x0000U}, // 142

{0x026EU, 0x0000U}, // 143

Kind regards,

Katherine