hello Hamza,

1) I'll try your new code shortly.

2) Under DAC5682z EVM Control. There's box " Digital logic: enable/disable" . Which option should I use?

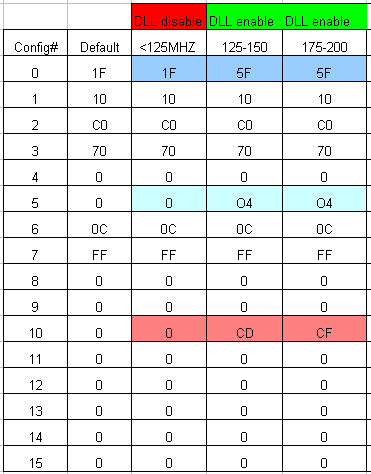

3) Could I set config.reg5681 as following for various clock frequencies. Please correct if settings are not correct.

thks,thu

(Attached this text for your modifications if needed)

| DLL disable | DLL enable | DLL enable | ||

| Config# | Deafult | <125MHZ | 125-150 | 175-200 |

| 0 | 1F | 1F | 5F | 5F |

| 1 | 10 | 10 | 10 | 10 |

| 2 | C0 | C0 | C0 | C0 |

| 3 | 70 | 70 | 70 | 70 |

| 4 | 0 | 0 | 0 | 0 |

| 5 | 0 | 0 | O4 | O4 |

| 6 | 0C | 0C | 0C | 0C |

| 7 | FF | FF | FF | FF |

| 8 | 0 | 0 | 0 | 0 |

| 9 | 0 | 0 | 0 | 0 |

| 10 | 0 | 0 | CD | CF |

| 11 | 0 | 0 | 0 | 0 |

| 12 | 0 | 0 | 0 | 0 |

| 13 | 0 | 0 | 0 | 0 |

| 14 | 0 | 0 | 0 | 0 |

| 15 | 0 | 0 | 0 | 0 |