Hi Team,

My customer is working on ADS8168 and they had few doubts regarding the serial interface of the same. Can you please help answer the below ?

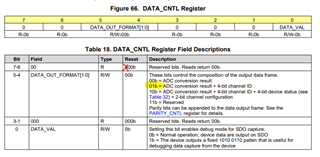

1) We need to update DATA_CNTL register of the device. We are transferring the following pattern to ADC. There is a confusion regarding the same. Please confirm whether its correct

a) Transfer "0x0800AA" (Register Access)

b) Transfer "0x081001" (Output bits as ADC Conv Result + 4 bit Channel)

2) The device is configured as slave and a microcontroller as master. The controller is configured to acquire data in multiples of 8 bits. We want to operate the ADC in autosequence and repeat mode. But to ensure the integrity, we want to retrieve the channel ID along with data. The "DATA_OUT_FORMAT" field of "DATA_CNTL" register can be configured to get both channel ID and ADC data by assigning it as 01b. But in that case the bit count will be 16 + 4 = 20. The controller is configured to acquire data in multiples of 8. It will send either 16 or 24 clock cycles before CS is turned high. So how can we solve this issue ?

Thanks,

Jash