Hello,

I'd like to ask some questions about AMC60704's IDAC output performance.

Questions

- The data sheet defines 0.4 V as the Min output compliance voltage of the AMC60704's IDAC, but what can happen if the IDAC output voltage goes below 0.4 V?

- I wonder if some parameters can go out of the specs but the device operates normally. Or, can the device show unexpected behavior? If the IDAC output voltage below 0.4 V is not allowed, the AMC60704 cannot be used for my design.

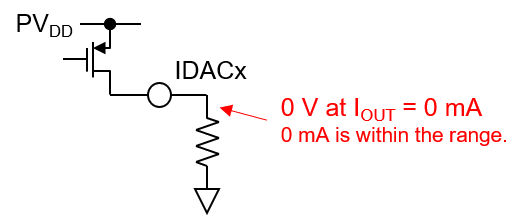

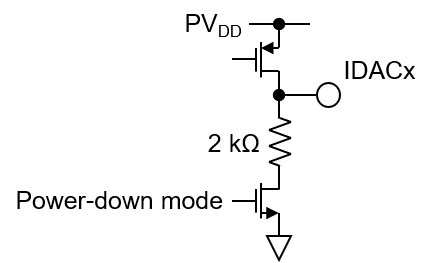

- In the application, a small amount of IDAC output current within the IDAC zero-scale error specs is suspected to flow out of the output from the observation of the load circuit's behavior when the current setting is 0 mA, but there is no means to confirm it. I'm wondering if an equivalent block diagram of the IDAC buffer amplifier is available because it could help identify the cause of the issue. Could you provide me with the IDAC buffer amplifier's equivalent circuit?

Best regards,

Shinichi Yokota