Other Parts Discussed in Thread: ADS1158

Hello,

I am using the ADS1258. the CLK frequency is 12.5 MHz, SCLK frequency is 1.5625 MHz.

The ADC is running in Auto-Scan mode. Te register condiguration is the following:

CONFIG0 0x56

CONFIG1 0x40

MUXSCH 0x00

MUXDIF 0x3F

MUXSG0 0x00

MUXSG1 0xF0

SYSRED 0x00

GPIOC 0x00

GPIOD 0x00

The sequence is:

1. Write ADC configuration

2. Send pulse convert command 0x80

3. Wait for conversion

4. Read channel data 0x30

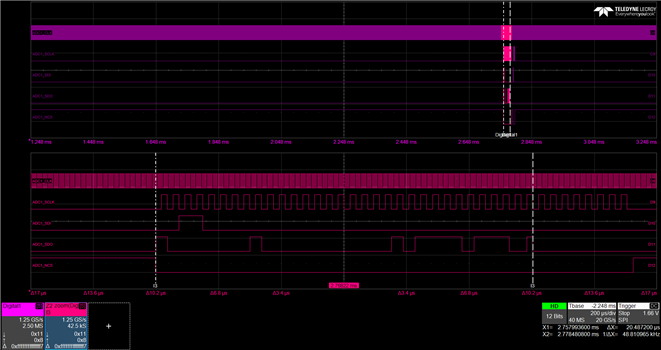

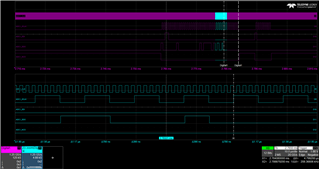

I see that the SPI interface sometimes goes into reset even when SCLK is active, missing the last byte of the channel data value.

The SPI goes into reset ~20,84 µs after the communication starts, that is 256 fclk cycles.

From the datasheet, I understand that the SPI interface should not go into reset while SCLK is active.

Have you observed this behaviour before?