Other Parts Discussed in Thread: ADS1278

Hello,

I am using two ADS1278 that are both part of the EVM-PDK kit, but using the MMB0 only for power. I have them configured in SPI daisy chain. They are both configured for high resolution mode and TDM/fixed output.

I am not able to make sense of the data that I am getting with the two parts in daisy chain. I was able to successfully read 8 channels from one part. Now I am trying to read 8 channels from one part and 4 from the other. I am looking at the signals to and from each chip to make sure things are working because I am not getting good data even from the U2 chip (using the naming from the datasheet figure 81) which I would assume would act basically as if it is not daisy chained for the first 8 channels worth of clocks.

What I am doing: I have slowed CLK to 512kHz to see if there are problems with my connections at high speed and that didn't seem to improve things but I am leaving it that way while I figure this out. I have not been power cycling the ADCs while testing this (maybe I have to do that?). When my MCU boots it

1. sets the SYNC pin high

2. enables the 512kHz clock

3. waits for 2^18/512kHz + 129/1kHz (0.641 seconds). This is my attempt to wait until data appears (as recommended by the datasheet) without reading the DRDY pin directly. This timing comes from Figure 84. Start-Up Sequence. and the note to wait until data ready before asserting SYNC is in the sentence immediately above that figure in the Feb 2011 revision of the data sheet.

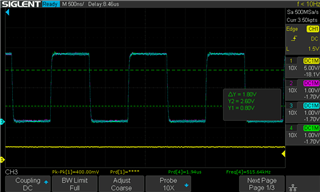

4. after data ready (really just a delay as described above) I bring the SYNC pin low for 10 us and then high again (CLK not stopped during this).

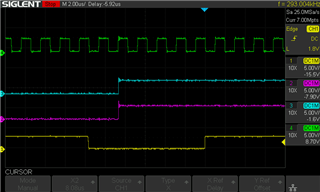

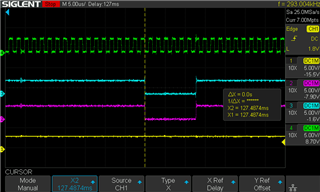

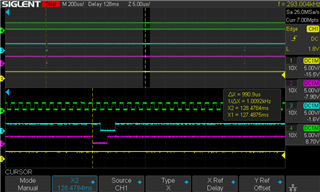

When I watch this on the scope I see that after bringing SYNC low and then high the DRDY pins from both chips stay high for about 129 Tdata periods as the datasheet says will happen. Then the first DRDY low edge from both chips is indeed aligned to the same clock falling edge as expected. However the next data ready pulse from the two chips is not aligned. I just did this and the DRDY falling edge from one chip (U2 as per the datasheet naming) was 3 clocks later than the DRDY falling edge from U1. As I let this run the DRDY edges do not remain in sync and shift in time with respect to each other.

The datasheet says I need to examine the DRDY pin from only U1, but I am wondering if I should expect that DRDY from both chips should remain in sync.

Perhaps there is something wrong with the way I am doing the sync operation?