Hi Ti Expert,

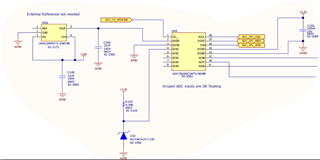

We are using ADC78H90 ADC to one of our important product line.

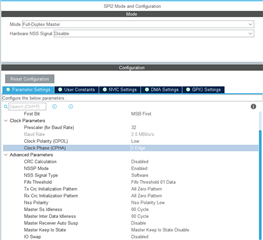

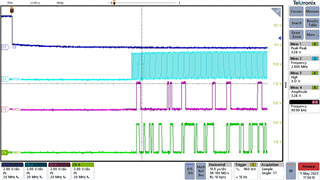

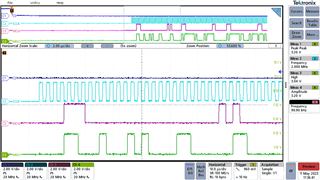

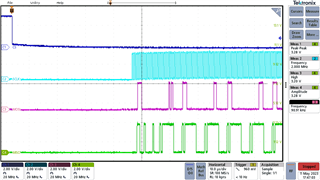

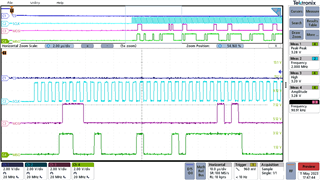

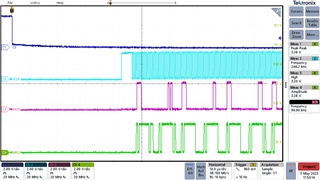

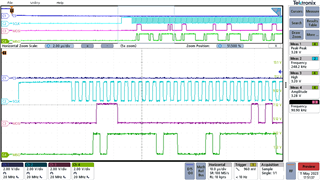

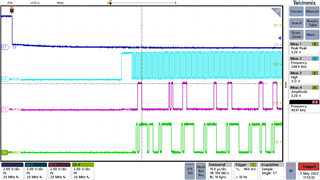

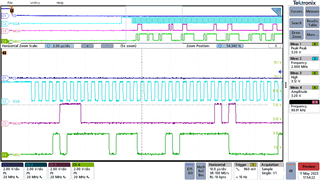

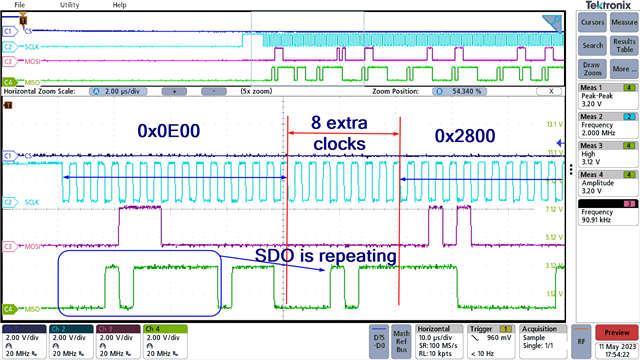

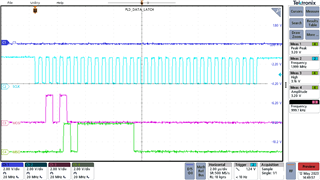

The interfacing of ADC78H90 to STM32H723VGT6 MCU over SPI communication is not working properly.

This is a showstopper for our R&D. Could you please kindly do the needful to support us to resolve the same?

Kindly let me know what information you need it.

We can have a online call also if needed.

Thanks.

Snehashis