Hi team,

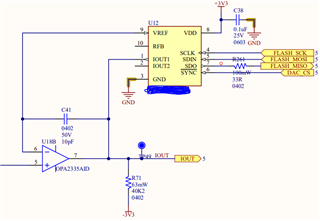

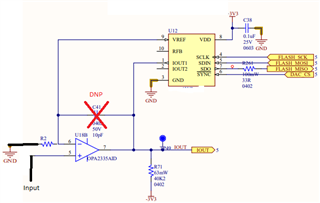

We are using DAC7811 in our project(through SPI communication) to control the gain of ADC signals. While working we noticed that the GAIN which we are trying to set is not applying currently. I have some doubts regarding this ,

1. Is there any sample code available for DAC7811 to control the gain through program ? , if yes please provide the reference here.

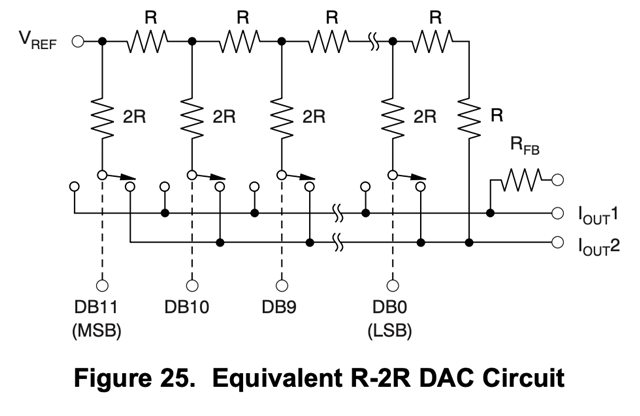

2. what is the default gain of this DAC7811( in datasheet it is mentioned like "The device powers on with zero-scale loaded into the DAC register and IOUT lines", does that mean the gain is zero?

3. the first 4 bits, i.e. C0- C3 is the main as per datasheet , there is a option for readback the DAC register or its value, if I write 0x2XXX where does it will provide me the readback value?

4. if I am not using daisy chain mode , is it mandatory to disable that while reading nd writing into DAC? , does this has any effect even though I am not using it.

regards,

Shikamaru