Hi team,

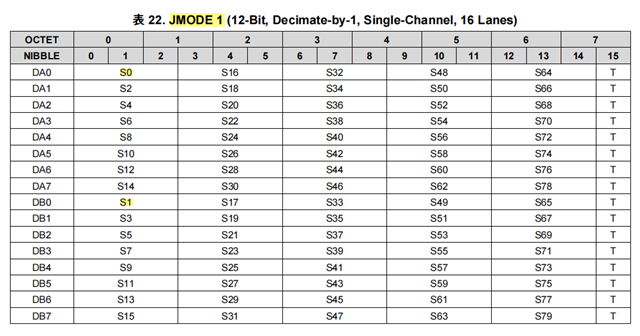

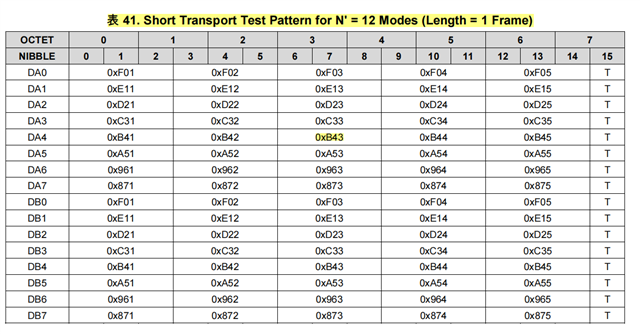

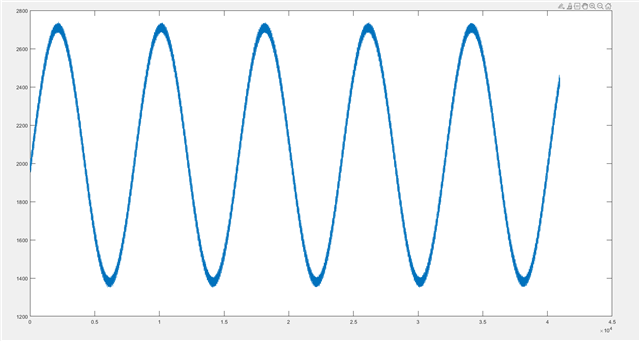

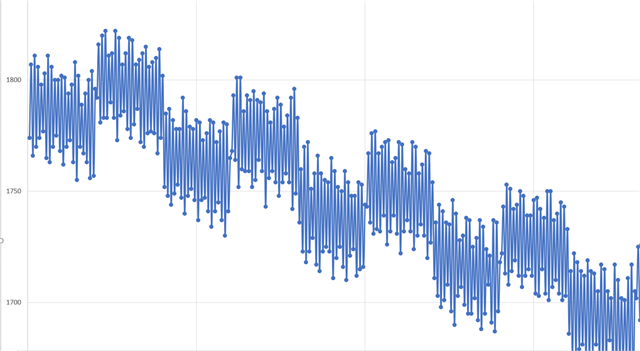

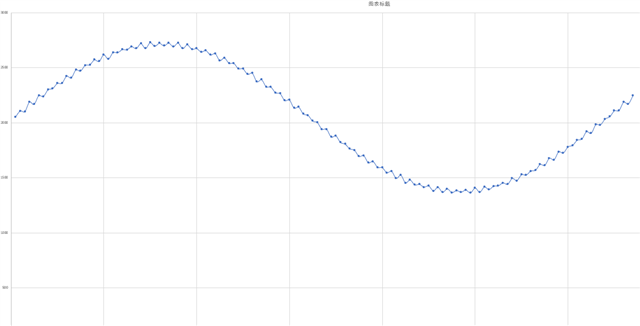

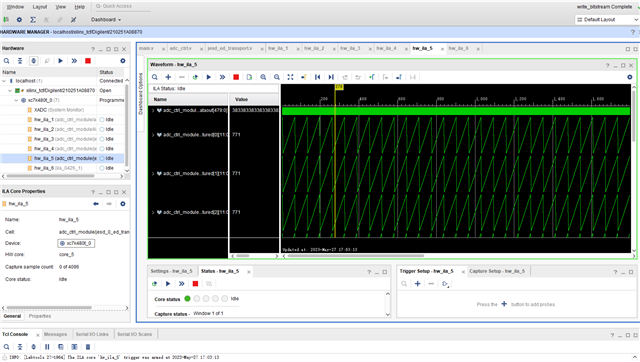

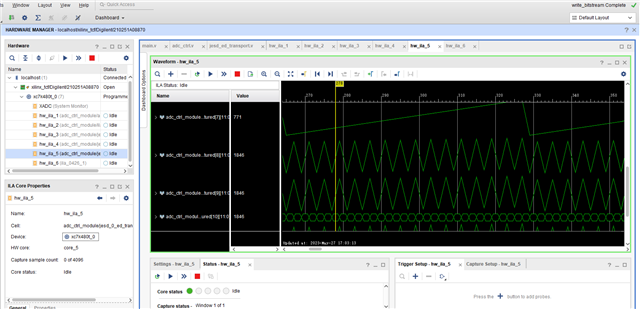

Set ADC to JMODE1 mode, lane_rate=6.4G, K=4, jesd204B_core lck=160MHz, Sysref is 20 MHz, sampling at 3.2 GHz, setting the ramp test mode. Checking the data through ILA, an error occurs starting with the ninth data, as shown in the following figure:

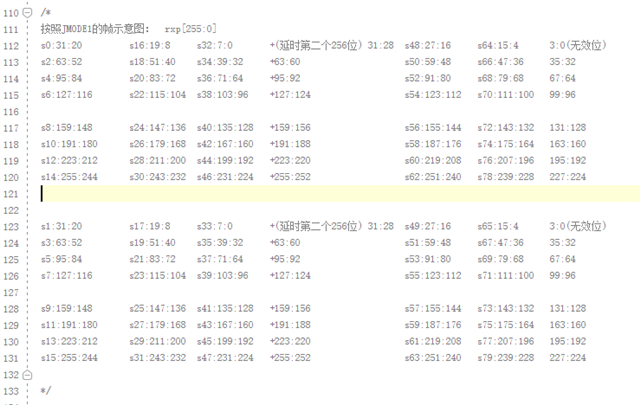

The following figure shows the data resolution:

Could you help check this case? Thanks.

Best Regards,

Cherry