Hi Team,

Customer is evaluating for our AFE5809 and having below questions about LVDS data output mode between I/Q and ADC, please help to answer:

- In customer’s configuration, LVDS serialized setting is 16bit, but for ADC data is 14bit. For FPGA LVDS receiver, does it will affect the switching between 16bit and 14bit LVDS? Or we need to make the training for LVDS?

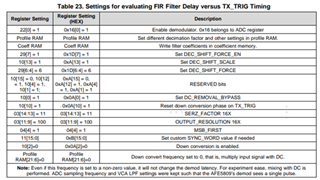

- What’s the time delay for I/Q LVDS to ADC LVDS mode?

- Regarding to I/Q, filtering, decimation factor etc. parameters, which one we can make the configuration in advance, and no impact from I/Q and ADC mode switching?

- If we configuration the I/Q parameter in advance, what’s the time delay for LVDS data output after other configurations?

- Do we have any suggestions for I/Q and ADC LVDS data mode switching and concerns in such case?

Thanks.