Other Parts Discussed in Thread: ADS1282, ADCPRO

Dear TI,

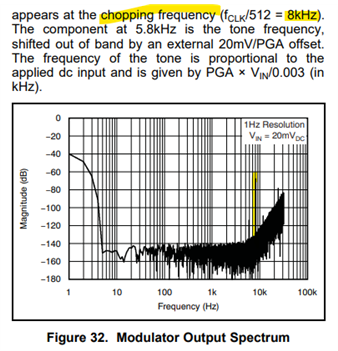

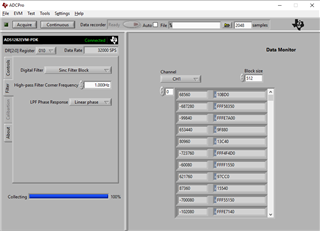

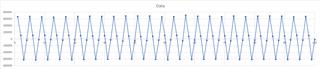

With the ADS1282EVM-PDK set up for shorted input measurements at a 32000 SPS rate (DR[2:0]=010, PGA=1, Preamp inputs shorted through 400Ohm resistor, sinc filter block) we are noting a repeating (high, mid, low, mid) pattern in the output data every four samples. An example data collection is shown below.

We also notice a similar pattern with the ADS1282 running in our circuit application.

Please forgive my ignorance regarding Delta-Sigma converters; is there a simple explaination as to why this occurs? I'd have thought that such a pattern shouldn't be observed at a divisor of either the master clock or sample frequencies.

Could I also please check: Is it the case that 64000SPS and 128000SPS modes aren't available in ADCPro because it's not possible to collect all 31 bits at this sample rate? Is it possible to get 24bit data at these rates using ADCPro?

Many thanks and best wishes,

Tom