Other Parts Discussed in Thread: DAC5687, DAC5686

Hi

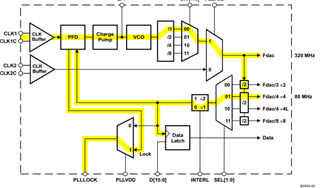

Im using the DAC5688 in PLL clock mode with CLK1 = 250 MHz and CLK2 = 250 MHz and the Frequency desired on PLL is 500 MHz (intp x2). For that M = 4 and N = 2. Sometimes i see a glitch or noise on my sine signal. I have a question about the reference clock for PLL.

If the CLK1 is 250 MHz, the input on PFD its already over the maximu frequency (160 MHz) ? or this parameter is for the feedback.

This block diagram is from the next application note : https://www.ti.com/lit/an/slwa040a/slwa040a.pdf. There is mencionated that the CLK2 its not used for DAC5686 and DAC5687. Its the same case for the DAC5688 ?

Regards,

Juan Camilo Peña