Hello,

I am using Pulse mode with continuous read. Everything is working well, I just can't reconcile the need for this delay with the datasheet. I am using a state machine in an FPGA, so I have good control over the timing. I found that I needed to introduce a delay between receivng the DRDY_N signal and reading the data. My understanding is that the DOUT should take the state of the DRDY_N upon assertion of the CS_N.

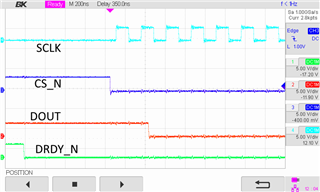

In this trace I have about 800 ns delay between DRDY_N and asserting CS_N. I need about twice that for it to read properly. The input is shorted, so the high order bits should be zero. You can see that the most significant bit is a one.

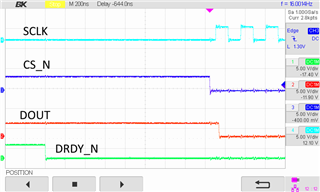

If I wait about 1.6 us, the data is correct.

I am meeting all my speed and accuracy requirements, so this isn't a big problem. I just don't understand it.

I'm using an external 8MHz clock.

START is asserted for 5 clock cycles. (625 ns)

SPICLK is 4 MHz.

Any ideas?

Thanks,

Chris