Hi all,

I have an issue on the ADS8353 ADC that I’d like to consult with you or maybe the factory about. I have been using this chip on other designs for many years and have never encountered this problem.

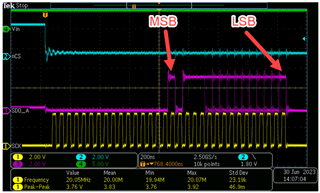

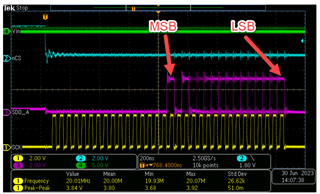

Basically, on some of our channels in one particular design, it looks like the MSB and the second-to-MSB are stuck at 1 and 0, respectively, regardless of what the input to the ADC is. I believe this always happens on both ADC channels in the chip. We are operating in 32-clock, dual SDO mode. AVDD is 5.1V; both references are 5.0V, and DVDD is 3.3V. I’ve checked all supplies and references on multiple boards, and they look good.

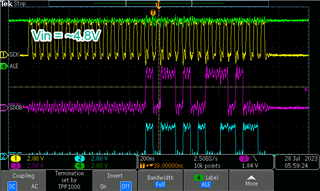

In the following scope plot, I’ve captured the channel A output code when the input to the ADC (green trace) is close to 5V. You can see the MSB is 1, as expected, but the next-to-MSB is 0, when it should be 1, since it represents the highest quarter of the ADC range.

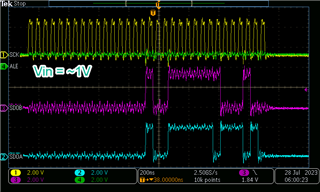

In this plot, I’ve captured the output code when the ADC input (green trace) is close to 0V. For inputs close to zero, I’d expect that most of the higher weight bits would be zero, but you can see that the MSB and next-to-MSB are the same as they were above, 1 and 0, when they should both be zero in this case.

You can see that those two bits never seem to move. It’s possible that this is a manufacturing issue, as we have most of the channels working normally. However, there are larger than expected number of channels that exhibit this same symptom, I’d say maybe 10-20%. (this is the first that I’ve probed the SPI to see what’s actually going on, but the behavior of the others is consistent.)

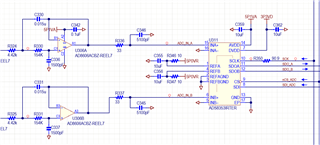

Also including a schematic screen grab of the ADC for reference:

The part markings on this particular ADS8353 specimen are:

8353

TI7A

PD1F

All ADC chips have the same markings, both those that exhibit this behavior and those that don’t.

Off the top of our heads, we’re thinking that maybe we somehow have the mode setup wrong when we’re programming the ADCs, or possibly edgy since most of them work ok? We are right at the clock spec limit (20MHz) but we’re used these parts for years at 20MHz without ever having seen this. Possibly a batch of these chips is more sensitive than others to clock frequency? Any other ideas?

Thanks in advance, Happy 4th if you're in the US, and look forward to hearing your thoughts!

Geoff