Hi,

We are facing some issues with TLV2548. In our board, we have 2 TLV2548 ADC's. It is communicating with Processor through SPI. While communication, we came to see that, ADC is misbehaving. Like we tried to set the initial configuration and provide the command for read back. In that case, we are not getting the proper results. for Eg: if we are setting the initial configuration as A000, During read back, its showing A080. Kindly let me know the issue.

we tested the same with aurdino , which worked fine. We also confirmed the spi interface of our processor by testing out another ADC of different make.

Could you please provide the linux driver/ Application code for the ADC " TLV2548CDW".

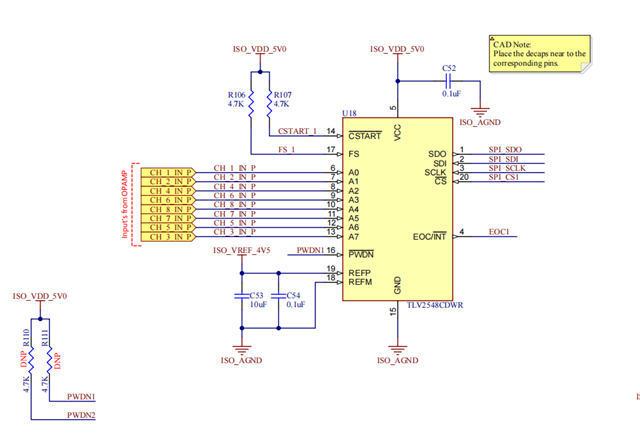

Attaching the Image of Schematics for referece.