Other Parts Discussed in Thread: ADC12D1620QML-SP,

Hello,

I would like you to confirm input condition of DESI and DESQ mode.

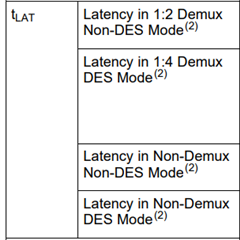

* According to datasheet, it seems that only "1:1 demux" and "1:4 mux" can be available on DES mode.

However, I understand that case of DESI and DESQ mode use only one ADC.

Therefore, I think that "1:2 mux" mode also can be available in above two mode. However, you describe only "1:4 mux" for multiplex mode of DES mode.

Is my understanding that user can realize "1:4 mux" even if they choose "DESI" and "DESQ" correct ?

Best Regards,