Hello,

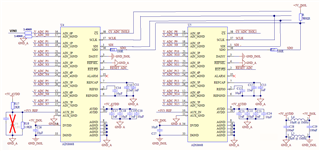

1. We are using 2 ADS8668 DACs in star topology. We have 2 separate CS that we control independently and we connect both SDO signals from the 2 DACs together (throug 100R series resistors), I attach the connection diagram. We have encounter SDO problems in this configuration:

* in one case one of the DACs broke and pulled SDO down continuosuly (we have cheked it by removing the series resistor).

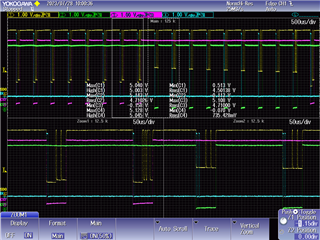

* In other case we have seen that the DACs are not able to carry SDO to 0V, when one of the DACs tried to put a '0' we have measured around 1V, when the other DAC tried to put a '0 we have measured around 2V. In all cases it worked fine for a period of time and start to malfunction after some time working. I attach an oscilloscope capture of this problem.

Can you please review the connection diagram and say if we are doing something wrong? Do you have any suggestion?

2. I have also a second question, we have 3k48 resistors in all ain_gnd pins to match impedance. But I have seen in datasheet that direct connection to GND is recommended. Would it be problematic to have it the way we have?