Hi Team,

What are the expected voltage levels when the TMSTP_LVPECL_EN is set to '1' ?

Can you tell me how the voltages of LVPECL fit with the requirement for common mode

please refer to section 6.3 - Recommended Operation Condition.

Thanks

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Team,

What are the expected voltage levels when the TMSTP_LVPECL_EN is set to '1' ?

Can you tell me how the voltages of LVPECL fit with the requirement for common mode

please refer to section 6.3 - Recommended Operation Condition.

Thanks

Hi Ohad,

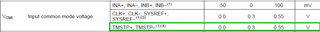

LVPECL here is bit of a misnomer. The common mode requirement when setting TMSTP_LVPECL_EN is set to '1' is as shown below.

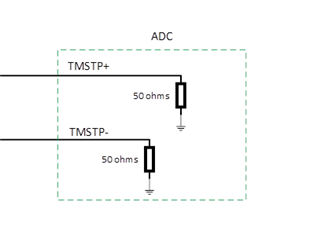

Each diff leg for TMSTP is connected to ground with 50 ohms.

Regards,

Neeraj