Hello Neeraj Gill Rob Reeder

request you to help us.

We are attempting to connect the Xilinx Zynq Ultrascale Board to the TRF1208-ADC12DJ5200RFEVM.

The following configuration has been made

1. To use External Reference clock mode, we updated the hardware in accordance with

the user guide instructions on page 16.

2. JESD setting in GUI:

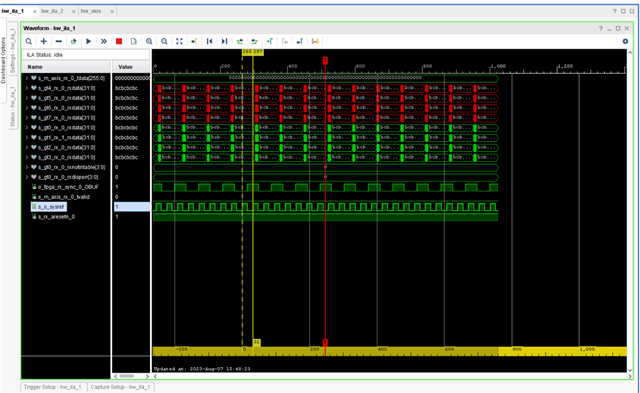

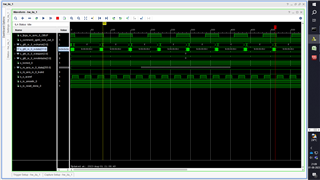

JMODE 2, Fs 3200MSPS, k =4 ,SYSREF = 10 MHz, FPGA_Clock = 320MHz,scrambling enable,auto sysref detection enable.

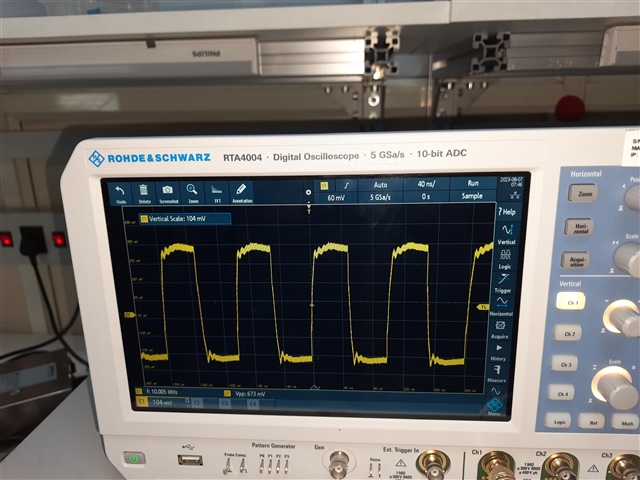

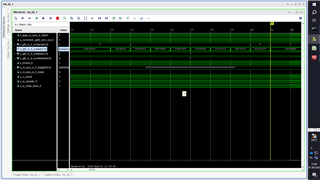

As shown in the figure, my sync is constantly toggling. Could you please assist me?

Thanks