Other Parts Discussed in Thread: TSW14J57EVM, , TSW14J58EVM, ADC12QJ1600EVM, LMK04828

Dear all,

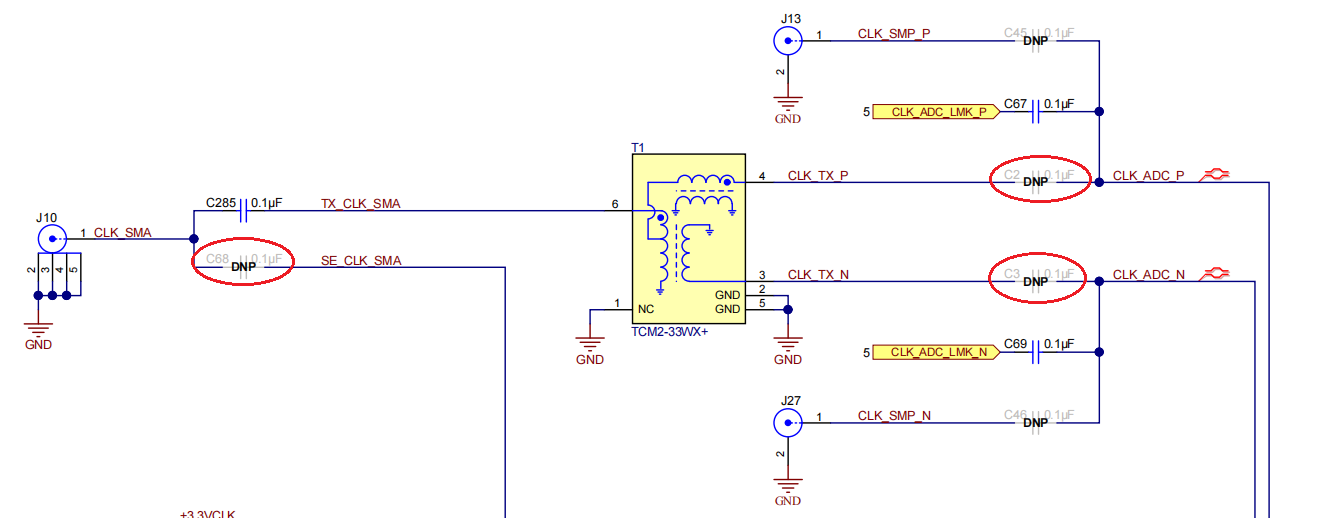

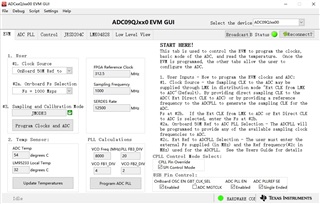

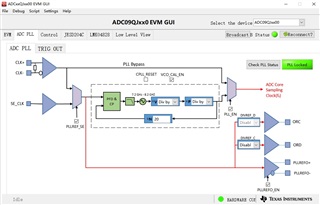

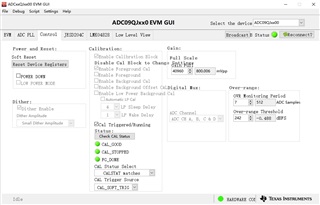

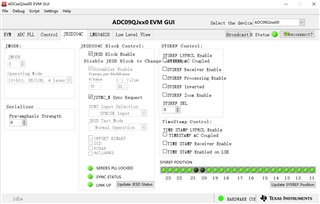

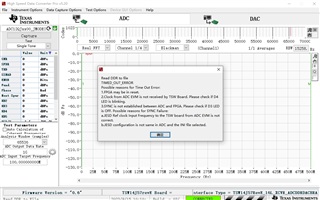

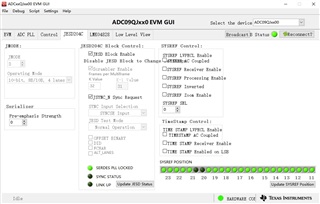

i am going to evaluate ADC09QJ1300EVM using TI's High Speed Data Capture/Pattern Generator Card; and TSW14J57EVM is easy to use, but it seems that TSW14J57EVM reference design needs external 1.6Ghz clock

connected with ADC09QJ1300EVM.

Is it possible to evaluate ADC09QJ1300EVM using TSW14J58EVM? So that i can evaluate ADC using onboard 50MEG clocking mode instead of external clock mode.

Testing Equipment for external clock source for High Speed ADC applications is not available for me at the moment;

Thanks a lot~~