Dear TI team

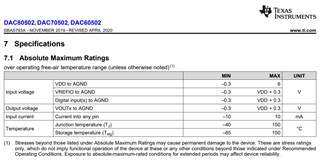

We have confirmed a waveform in which the VREFIO voltage momentarily exceeds "VDD + 0.3V".

The VOUT pin of the REF5050 and the VREFIO pin of the DAC80502 are connected directly without a resistor.

However, since this waveform is seen only momentarily when the power is turned on, we believe that there is no risk of damage to the device due to excessive heat.

Is this perception correct?

Best Regards,

Taroimo