Hi,

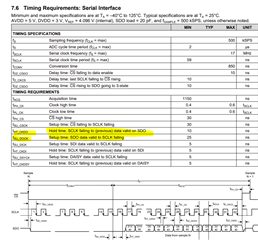

I wanted to get some clarification on the timing requirements for the SPI interface. On the datasheet, it talks about required setup and hold times for SDO (SPI output). What is it specifying? I don't believe outputs usually will have setup and hold requirements.

Thanks