After implementing CRC in all our devices utilizing eight DAC8760 units in a daisy chain configuration, we continue to experience long-term stability issues. It appears that our daisy chain intermittently "breaks" at unpredictable intervals, ranging from 5 days to 30 days, rendering all subsequent DACs inoperative until a power cycle and re-initialization occur.

We have refrained from enabling the watchdog function, and we are also not actively monitoring the alarm pin or the corresponding register.

Could you kindly provide clarification on the following points:

-

If the watchdog feature is enabled randomly on one or more DACs by the mentioned bit-pattern-bug, should this result in any changes in the mA output behavior or stop it?

-

In the event of an alarm being triggered, regardless of its cause, should this result in any changes in the mA output behavior or stop it?

-

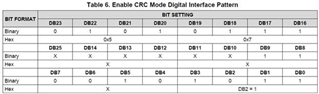

Is there a possibility that CRC functionality could be also disabled by a specific bit-pattern without pulling the Latch?

-

What precisely does the NO OP command to the CRC calculation? Shouldn't a full daisy chain data transmission (comprising 8 times 32 bytes in our setup) serve the same purpose of resetting the "SPI counter," whatever that means?

Urgent assistance is imperative, as we remain unaware of the potential number of devices deployed in sensitive areas that could abruptly cease updating their mA outputs. We are perplexed as to the root cause of these occurrences.

It is especially distressing since this marks the second occasion we have had to do debugging for weeks. On the previous instance, we found out about the CRC bug by sheer luck and subsequently painstakingly distributed firmware updates enabeling CRC communication to all our deployed devices across the globe.

We appreciate your prompt attention to this matter.