Other Parts Discussed in Thread: LMK04828,

Hello,

I'm including the previous thread here for background.

ADC32J25: JESD204B Configuration - Data converters forum - Data converters - TI E2E support forums

Also attached are

- TICS Pro file for LMK04828

- Schematic

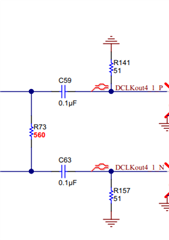

- LMK04828 circuit is on Sheet 18

- ADC32J25 circuit is on Sheet 15

- Photos of SYSREF outputs

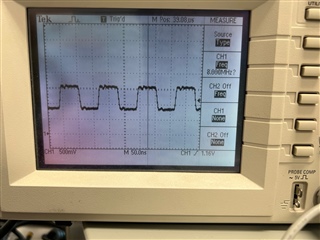

- SDCLKOUT1_sysref.jpg: sysref signal that goes to the FPGA

- SDCLKOUT3_sysref.jpg: sysref signal that goes to the ADC

- FPGA capture

- the waveform is continuous for 32 samples and goes thru a jump

- F=2 and K=32. Is there any conflict with SYSREF = 8 MHz (20x_?

Issues

- SDCLKOUT3 looks like a constant voltage at 2 volts. There is no 8MHz sysref observed.

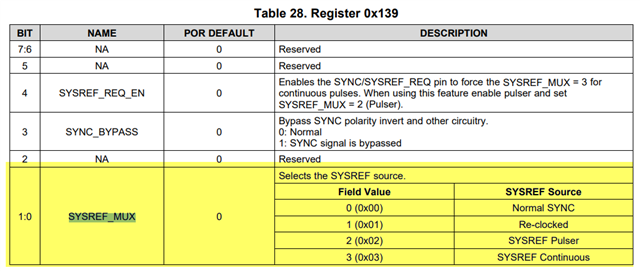

- SDCLKOUT1: I changed to 0x139[1:0] = 00 from 11 but the sysref is still repetitive at 8MHz.

We have verified sending the commands to the ADC and the FPGA is working.

- We can read back the ADC commands. We can make changes and the read back shows correctly

- LMK04828: DCLKOUT12 and SDCLKOUT13 are brought out to MMCX connectors for monitoring purpose. We can change the frequency from 160 MHz to 10 MHz or other frequency.

Could you advise on the issues with the SYSREF?

- no clock/pulse on SDCLKOUT1

- not being able to change to one-time on SDCLKOUT3)

Regards,

Andrew