Other Parts Discussed in Thread: ADS127L01

Hi Team,

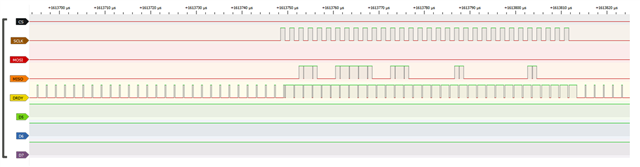

My customer have done some of the testing (SPI with 500khz SCLK) while they found out that sometime there are no data sent from TI ADS127L01EVM to MCU.

These “no data sent” issues usually will happen one or two times in between.

Please look at the picture attached below:

No data issue picture:

Please advise. Thanks!

Best Regards,

Ernest