Hi team,

I’m an analog FAE from east China and I’m supporting SUPCON.

Customer are testing DAC8740H to replace AD5700, and meet a question.

Test background:

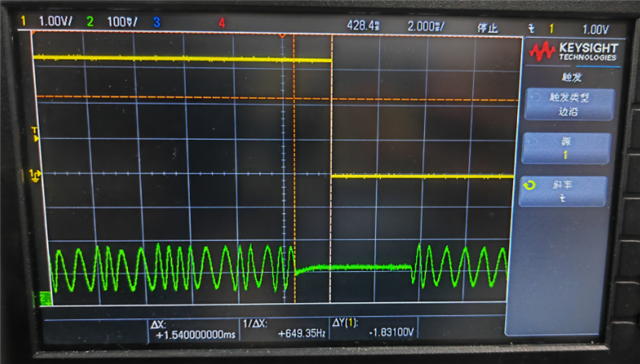

Customer use the upper computer to send Hart signal, through DAC8740H modulate, use the MCU to read UART result. Their software logic is that enable UART while catching the rising edge of CD pin, disable UART while catching the falling edge of CD pin.

Question:

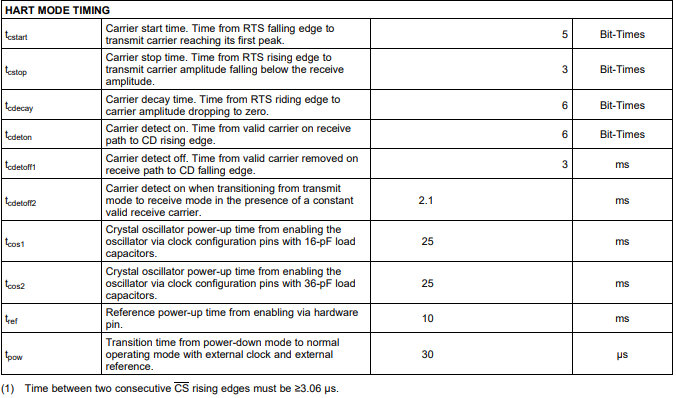

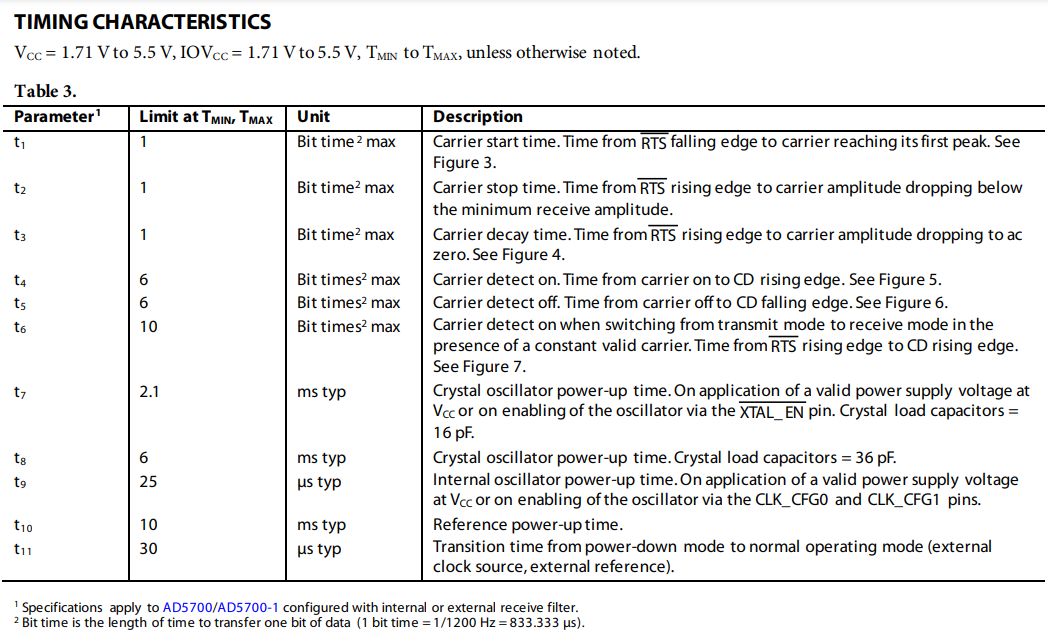

With DAC8740H, the UART signal is easy to lose the last bit. After debug, the root cause is CD pin pulled down too early, so UART was disabled and the last data transfer wasn’t complete. By checking the datasheet, DAC8740H has 3ms carrier detect off time while AD5700 has 5ms, can we extend Tcdetoff1? Or is there other methods to let CD pull down a little later?

DAC8740H Timing:

AD5700 Timing:

Pls kindly help me to resolve this time issue. BTW, I have also sent email to Joseph so that we can communicate more details by mail.

Thanks,

Severi Zhou