Other Parts Discussed in Thread: REF6025

This is the schematic I designed. Are there any areas that appear to be unreasonable or in need of correction?

My signal ranges from 0 to 20 Hz with a sampling rate of 200 Hz.

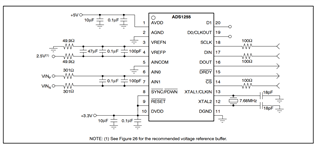

The following is the circuit diagram provided in the ADS1256 datasheet. I would like to know why there are so many decoupling capacitors connected to the VREF pin and their purpose.