Hi team,

Need clarification on the datasheet for this ADC, for a customer.

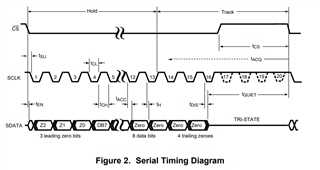

"It says that 16 clocks are required to transfer a sample. Three leading zeros, eight data bits, and four trailing zeros. This is 15. As near as I can tell by looking at the timing diagram, the chip tri-states the MISO pin prior to the master clocking in the final (16th) bit. To me this means three leading zeros, eight data bits, four trailing zeros, and an unknown bit."

Is this a correct interpretation? If so, what is the unknown bit? If not, what is the correct interpretation?

"Also, the data sheet says, "The sample bits (including leading or trailing zeroes) are clocked out on falling edges of SCLK, and are intended to be clocked in by a receiver on subsequent rising edges of SCLK." Clearly implying that the master captures the data on the rising edge. But, "If CS goes low before the rising edge of SCLK, an additional (fourth) zero bit may be captured by the next falling edge of SCLK." What is doing the capturing of the fourth zero bit?

Clearly there are two cases to consider. SCLK is low when CS goes low and SCLK is high when CS goes low. I'm guessing that in one case the master "captures" (on the rising edge) 3 leading zeros, 8 data bits, 4 trailing zeros and 1 garbage bit. In the other there are 4 leading zeros, 8 data bits, and 4 trailing zeros."

Thanks!