Hello, I used Xilinx FPGA and ADC09QJ1300 to complete the design of JESD204C. At present, I can see the IP output data of JESD204C of Xilinx in Vivado.

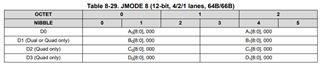

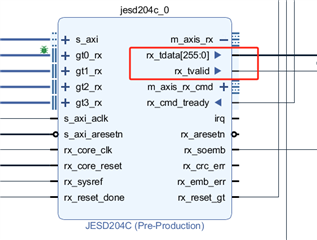

As shown in the figure, I use JMODE 8, and the output port of IP is a 256bit of data. As far as I know, in this 256bit, each channel takes up 64bit.

But I still don't know how to extract the samples in the 64Bit of each channel. I checked the [8.4.2.1 JESD204C Transport Layer Data Formats] section of the data manual, but I still don't understand how to process the data.

I want to get a clear indication, such as which bits to which in the 64bit data is sample information.

I have been reading it for many days, but I still don't understand it, so I came to ask for help, thank you very much for your help