Hello,

My customer is testing a board they designed using the ADS4249.

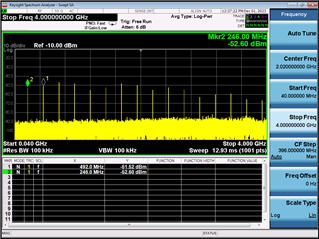

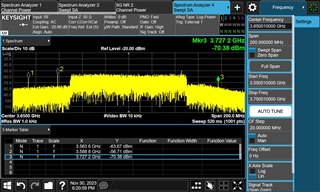

They say that the reference clock of 245.76MHz is observed at the RF IN port of ADS4249.

In what cases can symptom like this occur?

Is there a way to reduce the reference clock noise level at the RF IN port?

Thank you.

JH