Other Parts Discussed in Thread: TCA9537

Hello,

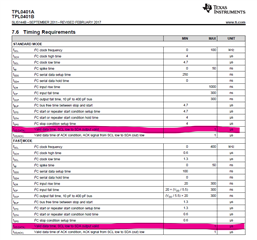

are the timing requirements in the table chapter 7.6 requiremens to the master µC that the TPL0401 will undestand the messages or is it just the timing, that the TPL0401 will generate when we read back the wiper position? I expect it is for both, because it also contains SCL values that will not be generated by TPL0401, right?

Will the TPL0401 automaticaly select between standard mode and fast mode? E.g if I use 95 kHz it could from frequency point of view work with both modes. If I measure for the µC I2C for tSPS 3,7 µs it would be ok for fast mode (>0,6 µs) but not for standard mode (>4 µs).

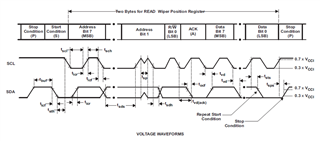

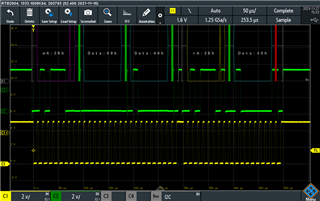

second more critical is with tVD (DATA) I have a bigger problem for both modes, in the datasheet is writen tVD (DATA) must be for both modes <1 µ, on the picture I expect it is marked as tvd (wihout Data but it is below the Data Bit 7) on Figure 9, right? But on the µC I measure at the moment depending on falling or rising edge 1,7 - 2 µs what would be longer than max value. On the answer Data we see that the tvd from TPL0401 is below the 1 µs.

Do you see here any issue? Isn't it more important, that the SDA Signal is valid High/Low befor SCL starts rising and not important that is is valid bevore 1 µs after the SCL is falling?

On our borads we did not see any communication problems until know, but we also did not check all edge cases like Temperature and so on.

Thank you for a fast answer.