Hello,

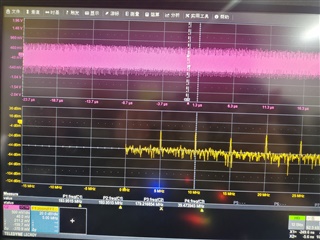

One customer used AFE5818EVM with FPGA to write command to test the data output by SPI, the sampling rate is 40Ms/s, output DCLK, FCLK and data are normal. But when he used signal generator to output 5Mhz, 5Vpp sinewave to channel1, the DCLK is unstable, it is about jumped between 200Mhz and 280Mhz, he did the FFT analysis, the result is as following, we could find that there is a lot of multi frequency peak value except 5Mhz.

Please help to analyze why caused this problem, if the write command is not correct?

Regards

kailyn