I need to verify the setup and hold times for SPI bus between TMS320 and ADS1263. I believe I found an issue with my design, where the SOMI setup time is not guaranteed by the ADS1263 datasheet. Could you please confirm whether I am understanding the datasheets correctly?

TMS320 Configuration:

SPI Port = A, SPIA CLK = 7.2MHz, High Speed Mode = Disabled, CPOL=0, CPHA=0 (Rising Edge Without Delay)

Based on CPOL and CPHA, data is updated on rising clock edge, and sampled on falling clock edge.

TMS320 SOMI Setup Time Requirement = 20nS (ref datasheet pg 163)

ADS1263 SOMI Setup Time Characteristic = (SPIA CLK Period / 2) - Tp(SCDO) = (138.89nS / 2) - 60nS = 9.44nS

SOMI Setup Time Margin = 9.44nS - 20nS = -10.56nS

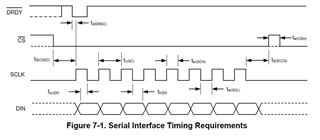

ADS1263 Timing Diagram: